Desarrollo de PCB

Utilice la estrategia de prueba adecuada desde el principio en el diseño de PCB

12/01/2021

Autor/editor: Dirk Müller*/Gerd Kucera

Dos tendencias en electrónica tienen una influencia decisiva en la estrategia de prueba para placas de circuito impreso: la miniaturización y el aumento de las tasas de datos. Esto significa que la capacidad de prueba de la PCB es un tema clave.

Empresas sobre el tema

Software FlowCAD EDA Vertriebs GmbH

Sistemas SPEA para electrónica profesional y automatización GmbH

NCAB Group Alemania GmbH

Imagen 1: ¡Atención! ¿El concepto de prueba también incluye cables que se colocan exclusivamente en capas internas en la prueba?

(Imagen: FlowCAD)

Las pruebas de PCB pueden representar hasta una cuarta parte del costo total de fabricación de productos electrónicos. La planificación temprana en el proceso de desarrollo de PCB permite minimizar estos costos. Las líneas en las capas internas de la PCB también deben tenerse en cuenta en el concepto de prueba obligatorio.

La continua miniaturización de los productos finales con placas de circuito cada vez más pequeñas, componentes más pequeños y restricciones de ubicación más estrictas está generando densidades de empaquetado electrónico más altas y la integración de otras tecnologías en el diseño. Las vías que atraviesan toda la PCB se realizan como vías láser ciegas y enterradas con un diámetro mucho más pequeño.

Estructuras rígido-flexibles reemplazan enchufes y conexiones de cables. Los componentes se colocan como componentes integrados en las capas internas de la placa de circuito impreso. Debido al nivel de voltaje reducido de la transmisión de señal moderna a alrededor de 1 V y una técnica de grabado más precisa en la producción de placas de circuito impreso, también se reducen los anchos de estructura de las pistas conductoras y sus distancias.

A medida que aumentan las tasas de datos, las normas para una calidad de señal determinada en la placa de circuito impreso se vuelven más complejas y restrictivas. Los niveles de voltaje y también los valores absolutos de voltaje para las tolerancias continúan disminuyendo. Hay más reglas de diseño a tener en cuenta al colocar las líneas de señal. Para evitar saltos de impedancia como fuente de problemas SI, las trazas solo pueden tener un ancho constante y un cierto espaciado para señales diferenciales.

Si no hay suficiente espacio para los puntos de prueba

Todo esto significa que ya no queda espacio para puntos de prueba en ninguno de los lados de una placa de circuito impreso, o no se permite el uso de puntos de prueba. Algunos diseñadores han intentado usar puntas para mover los puntos de prueba al lado de los componentes para que ya no estén cubiertos por la carcasa del componente. Otros diseñadores colocaron los puntos de prueba directamente en las líneas o intentaron derivar un punto de prueba de la línea de señal con stubs. Pero todos estos intentos tienen efectos negativos en la calidad de la señal con tiempos de subida más pronunciados de las señales o componentes de mayor frecuencia. Conducen a saltos de impedancia y, por tanto, a reflexiones en las líneas, o los ramales actúan como una antena para esta señal. Una matriz de puntos de prueba en un bus de direcciones y datos también afecta las impedancias de las líneas del bus.

Los PCB rígido-flexibles tienen muchas ventajas, sin embargo, la capacidad de prueba de este tipo de PCB es peor en comparación con las soluciones tradicionales. Con construcciones rígido-flexibles, las opciones de contacto para la prueba se reducen debido a los enchufes que se han racionalizado. El área flexible a menudo se excluye como superficie de contacto mediante una capa protectora y, por lo tanto, se excluye para los puntos de prueba. Para las vías en la transición de la zona rígida a la flexible, las zonas de bloqueo especiales, llamadas zonas de exclusión, dificultan las cosas. Reducen aún más las oportunidades de aplicar puntos de prueba.

El gran problema de la alta densidad de integración

Debido a las mayores densidades de integración en los componentes, la cantidad de pines en estos componentes también aumenta. Cada vez hay más señales que provienen de un BGA e inmediatamente se sumergen debajo del BGA en una capa interna de la placa de circuito impreso, donde se enrutan al siguiente BGA, donde también reaparecen debajo de un BGA. Cuando está equipado, esta señal ya no es accesible desde el exterior. Debido a la gran cantidad de señales bajo un BGA, una línea no se puede enrutar a un punto de prueba fuera del contorno del componente para cada señal, también porque el enrutamiento de las líneas de cinta en cada señal conduce a las antenas.

Puntos de prueba apropiados para los adaptadores de aguja

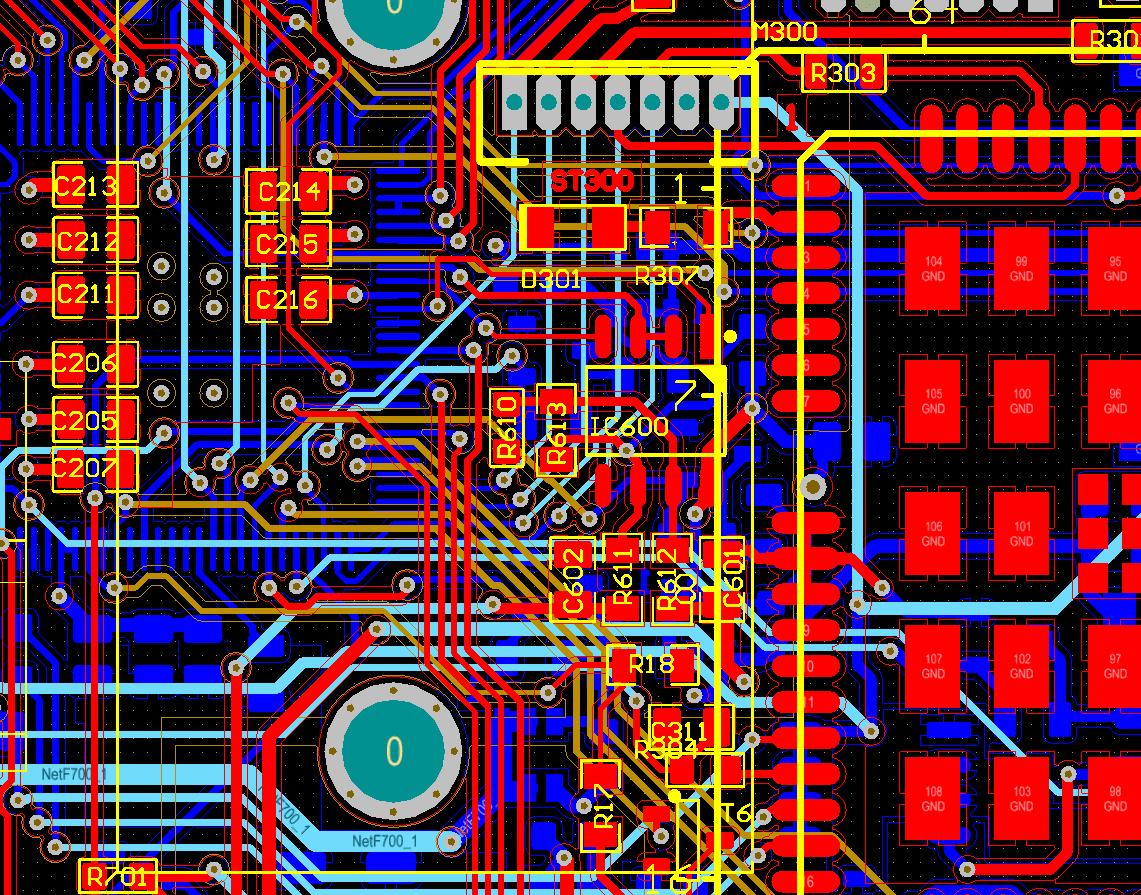

Imagen 2: estructuras de puntos de prueba inadecuadas para señales rápidas en la capa superior.

(Imagen: FlowCAD)

Para una prueba con adaptadores de agujas, solo queda la prueba en el estado sin equipo en un bareboard. Los puntos de prueba para agujas de prueba se pueden colocar en puntos de prueba adicionales o vías sin una capa protectora. Sin embargo, esto solo se aplica a las placas de circuito con señales lentas. Una vía es adecuada para la prueba. Sin embargo, si posteriormente se transmiten señales rápidas a través de esta línea durante el funcionamiento, entonces este revestimiento de orificio pasante es una antena. La longitud de una vía de arriba a abajo ya es demasiado larga para señales en el rango de Gbit. Un punto de prueba posiblemente se puede enrutar desde la primera capa interior a la capa superior a través de una microvía ciega.

Aunque colocar un punto de prueba en el extremo exterior parece un truco inteligente a primera vista, se debe verificar la velocidad de la señal y, por lo tanto, la longitud máxima del ramal. Dependiendo del tiempo de subida de la señal, la vía en el interior de la placa de circuito, que está en contacto por un lado, se convierte en una antena que emite señales o recibe interferencias.

La prueba de la placa de circuito a través de la interfaz JTAG

Imagen 3: Vía corta y larga (stub) para conectar puntos de prueba en capas internas.

(Imagen: FlowCAD)

Los fabricantes de componentes ya han abordado los problemas conocidos de la prueba. Los fabricantes de BGA comenzaron porque el problema de las señales sumergidas bajo el BGA se hizo evidente por primera vez aquí. Adjuntaron una interfaz JTAG al BGA, con la cual el BGA se puede cambiar a una autocomprobación desde el exterior. Este pequeño circuito de prueba, integrado en el silicio del chip, puede cambiar entre todos los pines y la función real en el IC.

Dos circuitos integrados pueden comunicarse entre sí a través de la interfaz JTAG y ejecutar un programa de prueba. Para ello, se realiza una conexión de prueba eléctrica desde el pin de medición de la interfaz JTAG a un pin del BGA. Lo mismo sucede en el segundo BGA, completando un circuito entre los dos pines de detección JTAG y la conexión entre los BGA. Con esta técnica, no solo se puede usar una interfaz JTAG para verificar si hay una conexión eléctrica presente, sino que también se puede probar la función de los componentes que están conectados entre los BGA, o también se puede medir el valor de una resistencia en serie.

Dependiendo del circuito, ya se puede lograr una alta cobertura de prueba con Boundary Scan. Aunque las líneas de autobuses JTAG también requieren espacio, se pueden colocar en capas internas y, por lo tanto, no se interponen en el camino del requisito de miniaturización. La interfaz JTAG ofrece otra ventaja, ya que también se puede utilizar para programar dispositivos.

La estrategia de prueba adecuada se encuentra rápidamente

Con la estrategia de prueba adecuada, el desarrollador puede decidir con anticipación qué redes se probarán y cuáles permanecerán sin probar. Puede tomar esta decisión en una etapa temprana junto con el diseño y la producción. Si las redes que deben probarse más adelante ya están definidas en el diagrama de circuito, se puede elaborar una estrategia común para la capacidad de prueba. Hay que tener en cuenta las normativas de prueba, que especifican, por ejemplo, el número de puntos de prueba en una red (0, 1 ó 2) y las distancias máximas que pueden tener los puntos de prueba de los pines de conexión. Por lo general, estas reglas se pueden asignar rápidamente a un grupo de redes en el Administrador de restricciones.

Reducir los puntos de prueba puede ser una alternativa

Si resulta que el ensamblaje contiene señales que no se pueden alcanzar a través de agujas de prueba, entonces se debe invertir la estrategia. Si se utiliza el escaneo de límites, entonces se debe intentar reducir tantos puntos de prueba como sea posible y probar las señales utilizando métodos de prueba de escaneo de límites y, al mismo tiempo, mejorar la calidad de la señal del circuito. En general, se requiere un equilibrio significativo entre los diferentes métodos de prueba.

Figura 4: Use el asistente DFT de XJTAG para registrar y administrar la cobertura de prueba de los diferentes métodos de prueba en el esquema.

(Imagen: FlowCAD)

El software gratuito DFT-Assistant de XJTAG detecta automáticamente qué señales son accesibles para una prueba JTAG en todo el esquema. Este software de XJTAG interactúa con herramientas EDA populares como OrCAD y Allegro de Cadence, así como con herramientas de Mentor, Altium y Zuken.

Los resultados se muestran como redes de colores en el esquema. El usuario puede elegir entre las categorías de exploración de límites "lectura, escritura, fuente de alimentación/tierra y redes sin acceso JTAG en el esquema". La cobertura de la prueba se muestra claramente en OrCAD Capture, por ejemplo, y se puede documentar fácilmente mostrándola y escondiéndola en el diagrama del circuito.

También puede leer este artículo en la revista especializada ELEKTRONIKPRAXIS número 1/2/2021 (Descargar PDF)

Las redes a las que no se puede acceder con JTAG requieren diferentes estrategias de prueba o se debe rediseñar el circuito. Existe una compensación entre los procedimientos, pasos y tiempos de prueba, el espacio disponible en la PCB y el impacto en la calidad de la señal. Por lo tanto, es recomendable planificar la capacidad de prueba junto con el diseñador de PCB y la producción al principio de la fase de desarrollo para encontrar el óptimo.

* Dirk Müller es director general de FlowCAD en Feldkirchen.

Archivos de artículos y enlaces a artículos

Enlace:

Boundary Scan y otras herramientas de FlowCAD

(ID:47020617)